Advancing DRAM Test Reliability: Circuit Design Breakthroughs

- admin

- 2023-12-07

- 1148

- Published in IEEE Transactions on

Instrumentation and Measurement (IF: 5.6, JCR: 86.5%) -

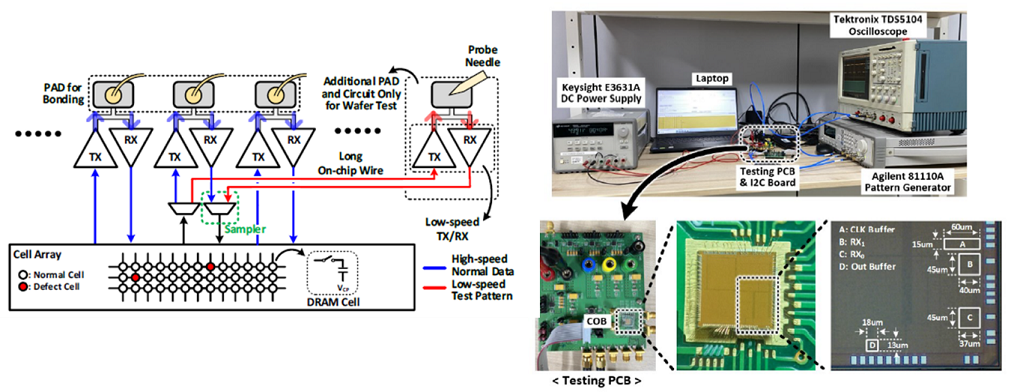

The

research team of Professor Juhyeong Chae (Department of Electronics &

Communications Engineering) successfully developed a circuit design technology

to improve the test reliability of low-speed wafer testing, which is part of

the DRAM mass production test processes.

The research was supported by government

funding (Ministry of Science and ICT) through the Institute for Information

& Communications Technology Promotion (IITP)’s 'PIM Artificial Intelligence Semiconductor

Core Technology Development Project' (2022-0-01013;

Edge Computing Enhanced DRAM PIM Semiconductor Technology Development,

2022-0-01037; High-performance PIM Memory Semiconductor Technology Development

based on DRAM), the 'Wireless Mobile Future Leading Technology Development

Project' of the National Research Foundation of Korea (NRF-2021M1B3A3102358;

Development and Demonstration of 433MHz-based Drone Communication Technology),

and support from the University's Excellent Researcher Support Program. The

research results were published in the prestigious international academic

journal, IEEE Transactions on Instrumentation and Measurement (IF: 5.6, JCR:

86.5%), under the title "Design of Clocked Comparator Preventing Bit

Errors to Improve Reliability of Low-Speed DRAM Measurement."

*Web Link: https://doi.org/10.1109/TIM.2023.3318687