-

[광운 Hot Issue] 채주형 교수(전자통신공학과) 연구팀, 반도체설계분야 세계최고권위 학술대회 ISSCC 2026 논문 채택 및 발표

조회수 267 | 작성일 2026.03.05 | 수정일 2026.03.05 | 홍보팀

-

채주형 교수(전자통신공학과) 연구팀, 반도체설계분야 세계최고권위 학술대회

ISSCC 2026 논문 채택 및 발표

- 차세대 LPDDR 메모리 인터페이스를 위한 데이터 수신 신기술 개발 –

본교 전자통신공학과 채주형 교수 연구팀은 차세대 LPDDR 메모리 인터페이스를 위한 데이터 수신 신기술을 개발했다. 해당 기술에 관한 논문은 2026 국제고체회로학술대회(International Solid-State Circuit Conference, 이하 ISSCC)에 채택되었으며, 지난 2월 18일(수) 성공적으로 발표를 진행하였다.

(좌측부터) 이기수 석사과정생, 한찬흠 박사과정생, 채주형 교수

이번 2026 ISSCC는 학회 출범 이후 가장 많은 논문이 접수되었으며 이에 따라 역대 가장 낮은 논문 선정율을 기록하였다. 반도체 설계의 총 12개 세부 분야에서 총 257개의 논문이 채택되고 발표되었으며, 이 중 한국의 채택 논문은 총 46편이다.

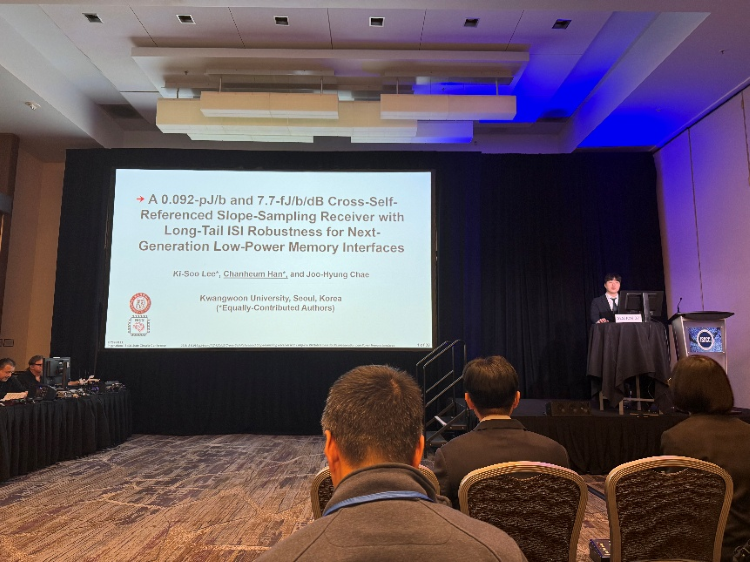

채주형 교수 연구팀의 논문은 이기수 석사, 한찬흠 박사과정이 공동 1저자로 집필하였으며, Session 37(Memory Interface)에서 한찬흠 박사과정이 발표를 진행하였다.

채주형 교수 연구팀의 2026 ISSCC 발표

채주형 교수 연구팀은 최근 다양한 응용 분야에서 전력 수요가 급증함에 따라 저전력 메모리인 LPDDR의 수요 또한 급증하고 있는 흐름에 주목했다. 연구팀은 LPDDR 메모리의 전력 효율과 데이터 송수신 성능 개선을 위한 새로운 연구 아이디어를 제안해 본 학회에서 많은 관심을 받았다.

한편, 세계 3대 반도체 학회 중 하나이며 반도체 설계 올림픽이라 불리는 ISSCC는 70여 년 전통의 반도체 회로설계 분야 세계 최대, 최고 권위의 학회로 전 세계의 기업, 연구소, 학교에서 3,000명 이상이 참석하여 매년 세계 최고 수준의 반도체 신기술을 발표하는 장이다.